|

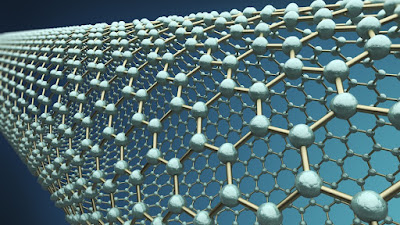

| Carbon Nanotube |

The breakthrough is that - IBM improves carbon nanotube scaling below 10nm. How ever before calling it as breakthrough we should also check out what other giants like Intel, AMD, TSMC or Samsung is working on. This breakthrough has relation with the Moore's Law. Yes you got right..!!It says that the transistor counts double only every 18 month or so. It’s the time that Intel marks 40 years of the 4004 microprocessor and here now lying some fear that progress will soon hit a wall.

You can refer to my post History and Evolution of Integrated Circuits where it shows clear progress of semiconductor industry.

But not to worry, IBM has developed a way that could help the semiconductor industry continue to make ever more dense chips to support Moore's law. These chips will be both faster and more power efficient.

Few glimpse of carbon nanotube transistors

- Carbon nanotube transistors can operate at ten nanometers

- Equivalent to 10,000 times thinner than a strand of human hair

- Less than half the size of today’s leading silicon technology

- Could also mean wearables that attach directly to skin and internal organs

Here I have an animation for Animated Nanofactory in Action.

As a result of this the devices will become smaller, increased contact resistance for carbon nanotubes has hindered performance gains until now.

These results could overcome contact resistance challenges all the way to the 1.8 nanometer node – four technology generations away.

A project at IBM is now aiming to have transistors built using carbon nanotubes ready to take over from silicon transistors soon after 2020. According to the semiconductor industry’s roadmap, transistors at that point must have features as small as five nanometers to keep up with the continuous miniaturization of computer chips.

IBM has previously shown that carbon nanotube transistors can operate as excellent switches at channel dimensions of less than ten nanometers – the equivalent to 10,000 times thinner than a strand of human hair and less than half the size of today’s leading silicon technology.

IBM's new contact approach overcomes the other major hurdle in incorporating carbon nanotubes into semiconductor devices, which could result in smaller chips with greater performance and lower power consumption.

Earlier this summer, IBM unveiled the first 7 nanometer node silicon test chip, pushing the limits of silicon technologies and ensuring further innovations for IBM Systems and the IT industry.

By advancing research of carbon nanotubes to replace traditional silicon devices, IBM is paving the way for a post-silicon future and delivering on its $3 billion chip R&D investment announced in July 2014.

IBM’s chosen design uses six nanotubes lined up in parallel to make a single transistor. Each nanotube is 1.4 nanometers wide, about 30 nanometers long, and spaced roughly eight nanometers apart from its neighbors. Both ends of the six tubes are embedded into electrodes that supply current, leaving around 10 nanometers of their lengths exposed in the middle. A third electrode runs perpendicularly underneath this portion of the tubes and switches the transistor on and off to represent digital 1s and 0s.

The IBM team has tested nanotube transistors with that design, but so far it hasn't found a way to position the nanotubes closely enough together, because existing chip technology can’t work at that scale. The favored solution is to chemically label the substrate and nanotubes with compounds that would cause them to self-assemble into position. Those compounds could then be stripped away, leaving the nanotubes arranged correctly and ready to have electrodes and other circuitry added to finish a chip.